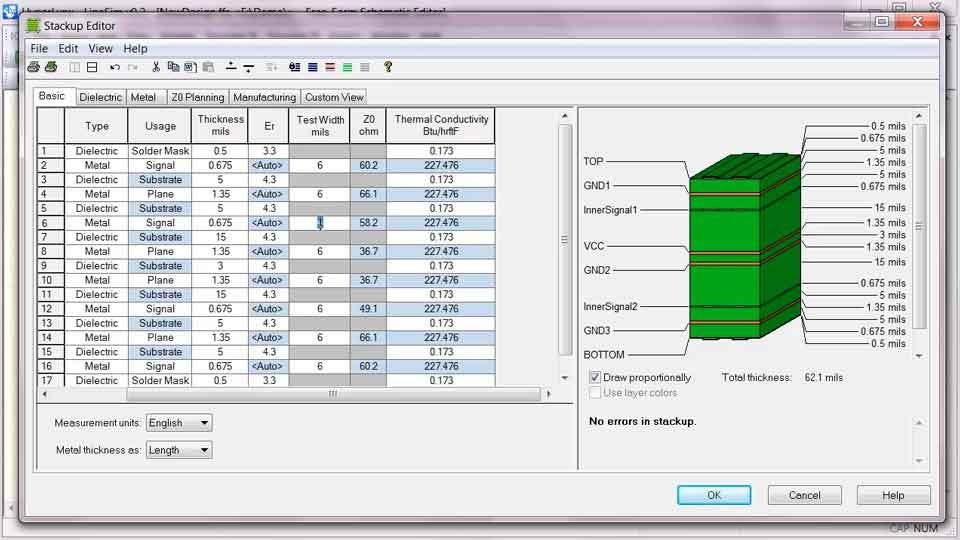

“Digital designers must learn new methodologies like channel operating margins (COM), pulse amplitude modulation with four states (PAM4), and hybrid memory cube (HMC) and other 3D memory architectures,” notes Mentor’s preview. On the stand during exhibition days (January 20 and 21, 12:30pm-6.00pm), Mentor will be running demos featuring capabilities and the latest HyperLynx innovations in SERDES channel optimization, power integrity analysis, electrical rule checking and 3D electro-magnetic extraction. This year’s conference takes place at the Santa Clara Convention Center.

The team behind Mentor Graphics’ HyperLynx PCB analysis and verification software suite will be out in force at next week’s DesignCon 2016 (January 19-21). Mentor’s PADS family extended for AMS, DDR and electrical DRC.Choose the right advanced packaging methodology for metal fill rules.HyperLynx made broader and easier to use.

0 kommentar(er)

0 kommentar(er)